## Hardware and Software Laboratory Project 3 (Hardware)

# "Design Flow Using CAD Tools"

Hardware and Software Laboratory Project 3 In Charge of Hardware Computer Science Course, School of Informatics and Mathematical Science, Faculty of Engineering, Kyoto University

## **Lecture Outline**

- Design flow using Quartus Prime (a CAD tool)

- How to use it for HDL design

- Writing to the FPGA and execution on an actual device

- Lecture structure:

- I will go give a semi-hands-on presentation using an adder as an example.

- If you get stuck on adder design, be proactive and ask a TA!

- If you can do it on your own, you can go ahead and get started on your design for a 7SEG LED drive circuit and counter for the introductory assignment.

- For those who forgot everything over spring break...

- http://www.lab3.kuis.kyoto-u.ac.jp/~takase/le3a/le2hw3-2019.pdf

## **Notes for AY2021**

- This document has been prepared to be compatible with the laboratory PC environment.

- Ubuntu 16.04 LTS

- Quartus Prime 17.1 Standard Edition

- ModelSim Intel FPGA Starter Edition 10.5b

- Please replace descriptions according to your own PC environment.

- The basics should not change much.

- If there are a lot of issues due to different PC environments, I'll let you know via Slack, etc. as required.

I'll use balloons to list the points that I know are important to keep in mind.

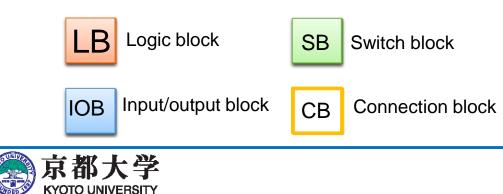

# **Review: What is an FPGA?**

- Field Programmable Gate Array

- An LSI whose contents can be modified (PLD: Programmable Logic Device)

- Can change the behavior of the hardware itself

- Allows you to form your own digital circuits freely as many times as you like

- The two major FPGA vendors: Xilinx, Altera (powered by Intel)

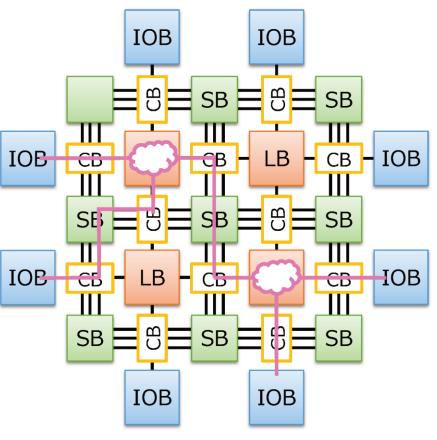

#### **Experimental Environment: FPGA Board**

- PowerMedusa MU500-RX/RK

- FPGA: Altera Cyclone IV EP4CE30F23I7N (28,840 LE)

- Microcontroller: Renesas RX210

- Clock: 20 MHz oscillator

- I/O User Interface

- ✓ Push SW x20, Rotary SW x2, 8bit DIP SW x2, Clock SW x1

- √ 7SEG LED x8, LED x8, Buzzer x1

- Expansion Board: MU500-7SEG

√ 7SEG LED x64, LED x64

## **Review: CAD Tools**

- Computer-Aided DesignTools to design and synthesize logic circuits

- They can do environment setup, circuit design and description, circuit synthesis, pin assignment, simulation, and programming (writing to FPGA).

- Also referred to as EDA (Electronic Design Automation) tools.

# **Experimental Environment: CAD Tools**

- Use "Intel Quartus Prime 17.1"

- Not the latest version (19.1)!

- The "Standard Edition" is already installed on the lab PCs.

- When searching Google for help, make note of the version number!

- $\checkmark$  Don't rely on the official manuals and documentation for other versions.

- You can install it on your own PC.

- The Lite Edition with limited functionality is available for free.

- Use ModelSim-Intel FPGA Starter Edition for the simulator.

The non-starter edition of Intel FPGA requires a paid license.

- $\checkmark$  See the supplement on the next slide for more details.

- Windows/Linux only (Not compatible with macOS)

# **Supplement: Installing Quartus Prime**

- How to install Quartus Prime 17.1 Lite Edition

- Download the installer for 17.1 Lite Edition. https://fpgasoftware.intel.com/17.1/?edition=lite

- $\checkmark$  You need to create an Intel account.

- ✓ You will sometimes get a "Legal Disclaimer" warning you that it is not the latest version. Ignore the warning and just click "I Agree."

- $\checkmark$  The "batch file" is 5.8 GB.

- ✓ If you're downloading the "individual files," download the following to the same location on your drive (total 3.2 GB).

- Quartus Prime (includes Nios II EDS)

- ModelSim-Intel FPGA Edition (includes Starter Edition)

- Cyclone IV device support

- (continued on next page)

# **Supplement: Installing Quartus Prime**

- How to install Quartus Prime 17.1 Lite Edition

- In the case of "individual files," please place the three files in the same location.

- Start the installer and run it with the appropriate checkboxes checked.

- $\checkmark$  The installation directory should be the default (the explanation in these slides assumes the default location).

- $\checkmark\,$  In Select Components, the following must be checked.

- Quartus Prime (includes Nios II EDS)

- Devices > Cyclone IV

- ModelSim Intel FPGA Starter Edition

- » NOT ModelSim Intel FPGA Edition!!

- If you are using Windows, please also install the USB Blaster II device driver that appears after the Quartus installation is complete.

- ✓ If the USB cable of the FPGA board is not recognized properly, please refer to this page.

# **Supplement: Installing Quartus Prime**

- Installation of Quartus Prime on your PC

- The Lite Edition with limited functionality is available for free.

- The ModelSim-Intel Starter Edition is a simulator that is available for free.

- $\checkmark$  The non-starter edition of ModelSim-Intel requires a paid license.

- What is the difference between editions?

- The Standard Edition, which is the same as the one installed on the lab PCs, is a 30-day trial.

- Pro Edition is not available (Cyclone VI equipped on board is not supported).

- There is no significant difference at the level of use in this exercise, except that Lite does not have "multi-processor support."

- $\checkmark$  Multi-processor support can reduce the compile time for synthesis. Other differences

- Synthesis performance and optimization results may differ between editions.

- When writing your report, please specify the edition used.

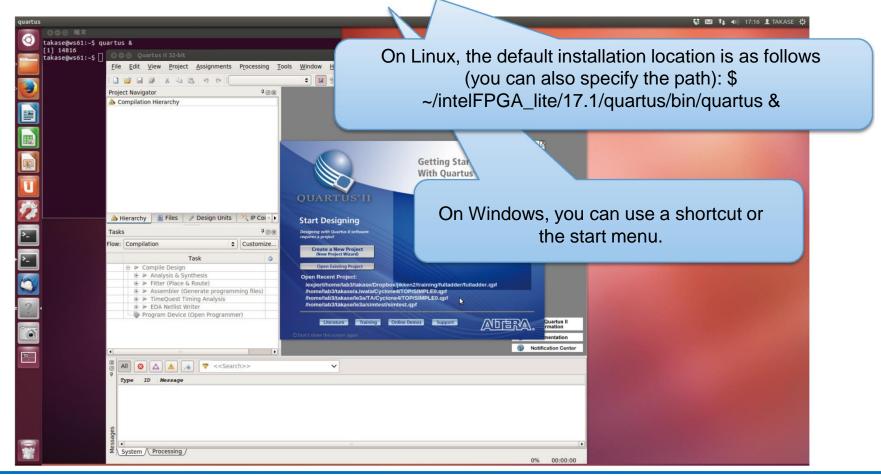

## **Boot up Quartus**

• In the terminal, type \$ quartus &

# **Check Your Settings**

The Lite Edition does not require any license settings. Select 'Run the Quartus Prime software' when prompted at the first startup.

#### Activation

- Tools -> License Setup... Make sure you are not getting a "Not found" message.

- If it says "Not found" or "License Setup Required" appears at startup, enter "27000@is-fpg-00" in the "License file:" field, or check "LM\_LICENSE\_FILE variable:" and enter it.

- Web browser settings

- Navigate to Tools -> Options, then Internet Connectivity... and set the path to your preferred browser in "Web browser:" field.

- If you don't have any preference, use "/export/share/bin/firefox."

- ✓ This is useful during error checking.

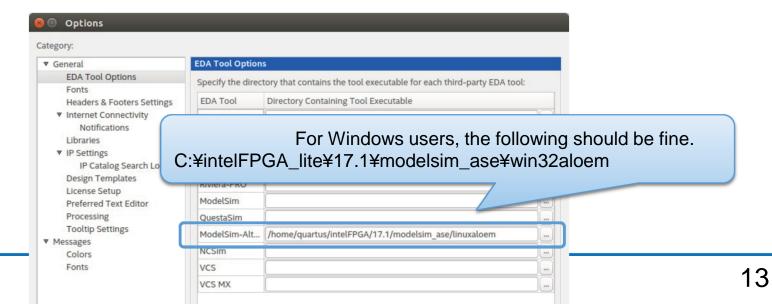

# **Check Your Settings**

- Configure the settings to call modelsim-ase from Quartus.

- Tools -> Options... -> EDA Tool Options: ModelSim-Altera: /home/quartus/intelFPGA/17.1/modelsim\_ase/linuxaloem

- ✓ Note that the 's' may be missing.

- ✓ You can leave it blank for the moment.

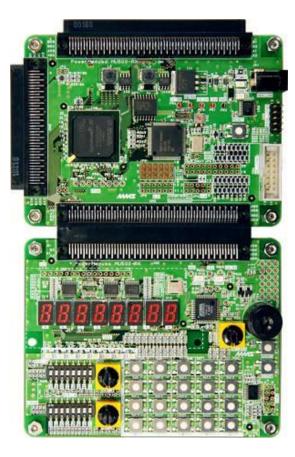

# **Tool Use and Design Flow**

- a. Creating a New Project and Configuring the Environment

- b. Logic Circuit Design

- c. Creating HDL Code

- d. Compilation

- e. Setting and Verifying Timing Constraints

- f. Verifying Operation via Simulations

- g. Assignment of I/O Pins to Top-Level Circuits

- h. Writing the Circuit to the FPGA

The design flow is explained using a 4-bit adder as an example.

This project is a combinational circuit, so this step is not needed.

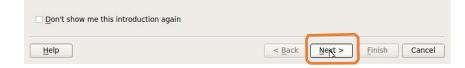

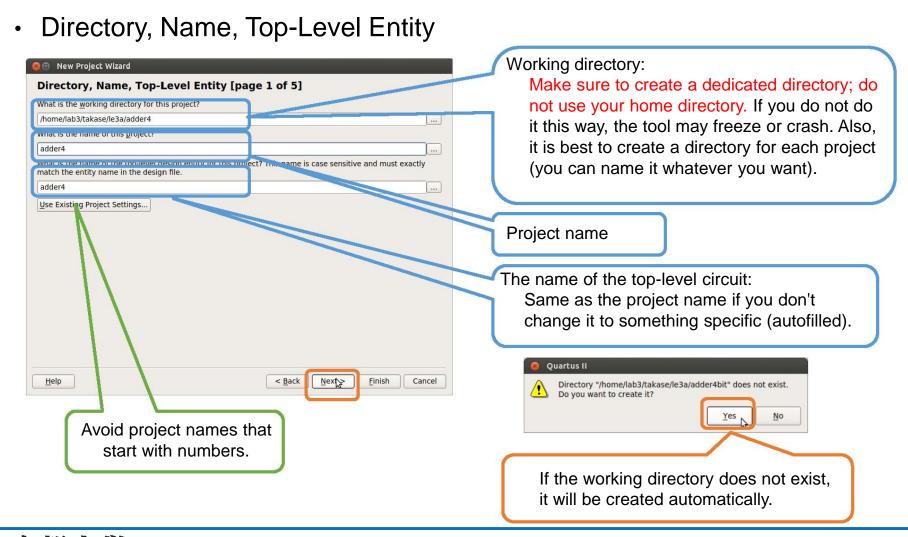

- File -> New Project Wizard...

- Introduction "Next"

| 🕒 New Project Wizard |

|----------------------|

|----------------------|

#### Introduction

The New Project Wizard helps you create a new project and preliminary project settings, including the following:

- Project name and directory

- Name of the top-level design entity

- Project files and libraries

- Target device family and device

- EDA tool settings

You can change the settings for an existing project and specify additional project-wide settings with the Settings command (Assignments menu). You can use the various pages of the Settings dialog box to add functionality to the project.

| Fil | e <u>E</u> dit | View    | Project    | Assignments | P | roc |

|-----|----------------|---------|------------|-------------|---|-----|

|     | <u>N</u> ew    |         |            | Ctrl+N      |   | -   |

| 2   | <u>O</u> pen   |         |            | Ctrl+O      |   | 1   |

|     |                |         |            | Ctrl+F4     |   | 1   |

|     | New P          |         | ard        |             |   |     |

| Cà  | Open Pro       |         |            | Ctrl+J      |   |     |

|     | Save Pro       |         |            |             |   |     |

|     | Close Pro      | oject   |            |             |   |     |

| M   | Save           |         |            | Ctrl+S      |   |     |

|     | Save As.       |         |            |             |   |     |

| 9   | Save All       |         |            | Ctrl+Shift+ | s |     |

|     | Eile Prop      | erties  |            |             |   |     |

|     | Create [       | Update  |            |             | • |     |

|     | Export         |         |            |             |   |     |

|     | Convert        | Progran | nming File | s           |   |     |

|     | Page Set       |         |            |             |   |     |

| 4   | Print Pre      | view    |            |             |   |     |

|     | Print          |         |            | Ctrl+P      |   |     |

|     | Recent F       | iles    |            |             | • |     |

|     | Recent P       | rojects |            |             | • |     |

|     | E <u>x</u> it  |         |            | Alt+F4      |   | Cu  |

|     | 17             |         | -          | ask         |   | -   |

- Project Type: Select "Empty project"

- · Add Files: Add already created circuits to the project.

- This time, there is nothing to add, so leave it blank and click "Next."

- Family & Device Settings

- Family:

"Cyclone IV E"

Available devices:

"EP4CE30F23I7"

| New Project Wizard<br>amily & Device Sett                             | ings (pag      | le 3 of   | 51                    |              | onvenie    |            |            |

|-----------------------------------------------------------------------|----------------|-----------|-----------------------|--------------|------------|------------|------------|

| elect the family and device you<br>ou can install additional device s | want to targe  | t for com | pilation.             | nd on the T  | ools menu. |            |            |

| Device family                                                         |                |           | Show in 'Availa       | able devices | ' list     |            |            |

| amily: Cyclone IV E                                                   |                | \$        | Package:              | Any          |            | 1          | \$         |

| Devices: All                                                          |                | ¢         | Pin <u>c</u> ount:    | Any          |            | 1          | \$         |

| Target device                                                         |                |           | Sp <u>e</u> ed grade: | Any          |            |            | \$         |

| <ul> <li>Auto device selected by the Fitter</li> </ul>                |                |           | Name filter:          | EP4CE30F     |            |            |            |

| Specific device selected in 'A<br>O Other: n/a                        | wailable devid | es' list  | ✓ Show adva           | nced device  | s 🗌 HardC  | Copy compa | tible only |

| ailable devices:                                                      |                |           |                       |              |            |            |            |

| Name Core Velta                                                       | go LEc         | User      | WOs Mom               | ory Dito     | Embodd     | ed multipl | ier 0 bit  |

| P4CE30F23I7 1.2V                                                      | 28848          | 329       | 608256                |              | 132        |            |            |

|                                                                       | 20040          | 220       | 600256                |              | 112        |            | Þ          |

|                                                                       |                |           |                       |              |            |            |            |

| ompanion device                                                       |                |           |                       |              |            |            | \$         |

|                                                                       |                |           |                       |              |            |            |            |

| Companion device<br>HardCopy:<br>Limit DSP & RAM to HardCop           | v device reso  | urces     |                       |              |            |            |            |

You can also apply a filter

17

- EDA Tool Settings

- Specify if you want to use/modify external design tools.

- Specify the HDL to be used in the "Simulation" step.

/home/lab3/takase/le3a/adder4bit

adder4bit

adder4bit

Cyclone IV E

EP4CE30F23I7

<None> (<None>)

ModelSim-Altera (Verilog HDL)

< Back

0

0

()

1.2V -40-100 °C

• Summary

New Project Wizard

Summary [page 5 of 5]

Project directory:

Top-level design entity:

Number of files added:

Device assignments: Family name:

Device:

EDA tools:

Number of user libraries added:

Design entry/synthesis: Simulation:

Junction temperature range:

Timing analysis: Operating conditions: VCCINT voltage:

Project name:

- Confirm the settings and click "Finish."

When you click Finish, the project will be created with the following settings:

| Tool Type      | Tool Name         | Format(s)        | Run Tool Automatically                              |

|----------------|-------------------|------------------|-----------------------------------------------------|

| Design Entry/S | <none></none>     | <none></none>    | Bun this tool automatically to synthesize the curre |

| Simulation     | ModelSim-Altera 🗘 | Verilog HDL      | R n gate-level simulation automatically after comp  |

| Formai verinc  | <none></none>     | L2               |                                                     |

| Board-Level    | Timing            | <none> 🖨</none>  |                                                     |

|                | Symbol            | <none> 🖨</none>  |                                                     |

|                | Signal Integrity  | <none> 🗘</none>  |                                                     |

|                | Boundary Scan     | <none> \$</none> |                                                     |

|                |                   |                  |                                                     |

Next Einish Cancel

# **b. Logic Circuit Design**

- Think about the logic circuit you want to design.

- External specifications: I/O, functions

- Internal specifications: Circuit configuration

- ✓ Truth tables, Karnaugh maps, state transition diagrams, etc. → Logic formula expression

- → There is no need to go into this much detail in HDL design, but you should think long and hard about what kind of HDL code you want to write.

First think about the design, then start using the tool!

- External specifications of 4-bit adder

- Input: 4-bit additive data, 1 bit of carry-in

- Output: 4-bit sum, 1-bit carry-out

# c. Creating HDL Code

Avoid file names that

start with numbers.

- Use the HDL editor.

- File -> New -> Verilog HDL File or File -> New -> VHDL File

- ✓ Select it according to the HDL you want to use.

- Have fun designing with hardware description languages in Experiment 3!

- $\checkmark$  You can also combine with circuit diagrams.

- If you make top level circuit diagrams and components in HDL, it will improve the overall visibility.

- First (before you end up crying), save the HDL file.

- File -> Save As...

- "adder4.v"

- ✓ For VHDL: "adder4.vhd"

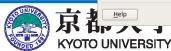

- Set the "Flow:" in the Tasks window to "Compilation."

# c. Creating HDL Code

- Configuration of the (initial) window

- The layout and size of the windows can be adjusted as appropriate to suit your needs via View -> Utility Windows, etc.

- The editor function is lacking, so you may use your preferred editor (synchronize files with external tools at your own risk).

# c. Creating HDL Code

Example for Verilog HDL

Example for VHDL

|        | adder4.vhd 🗙                                       |

|--------|----------------------------------------------------|

|        | 😒 Z 0 🕺 0 0° °0 0 🕸 🕸 🐔                            |

| 1      | library IEEE;                                      |

| 2      | use IEEE.std_logic_1164.all;                       |

| 3      | <pre>use IEEE.std_logic_unsigned.all;</pre>        |

| 4      |                                                    |

| 5      | entity adder4 is                                   |

| 6      | E port (                                           |

| 7      | <pre>a, b : in std_logic_vector(3 downto 0);</pre> |

| 7<br>8 | cin : in std_logic;                                |

| 9      | <pre>sum : out std_logic_vector(3 downto 0);</pre> |

| 10     | - cout : out std_logic );                          |

| 11     | end adder4;                                        |

| 12     | L                                                  |

| 13     | architecture adder4 body of adder4 is              |

| 14     | L signal tsum : std_logic_vector(4 downto 0);      |

| 15     | Ebegin                                             |

| 16     | tsum <= ('0' & a) + ('0' & b) + cin;               |

| 17     |                                                    |

| 18     | $cout \leq tsum(4);$                               |

| 19     | <pre>sum &lt;= tsum(3 downto 0);</pre>             |

| 20     | end adder4 body;                                   |

| 21     |                                                    |

2

- Convert to configuration information of logic blocks in FPGA (equivalent to C compilation).

- Convert circuit diagrams to register transfer level.

- Perform logic synthesis, technology mapping, and placement/wiring.

- ✓ Assign RTL-described circuits to logic blocks on the FPGA, then place and wire the logic blocks.

- Generate a bitstream.

- ✓ Convert placement/wiring information into a binary configuration information file.

- Compilation procedure

- Processing -> Start Compilation or Start Compilation on Tool Icons or Ctrl+L

- $\checkmark$  Only an input check is possible with Start Analysis & Synthesis.

- If all of the

under "Compilation" in the Tasks window are green, the compilation is successful.

- A yellow ? indicates that the flow requires recompilation.

- A red  $\times$  indicates that an error has occurred in the flow.

- If the flow does not terminate normally, check the message window at the bottom or messages found at "Compilation Report -> Flow Messages" and debug based on the messages.

- Right-click Help to allow online access to messages.

- You also need to check Critical Waning/Warning.

*(YOTO UNIVERSITY*

✓ Warnings tend to be quite relentless in CAD tools, but only ignore warnings if you understand the meaning (often they help to discover design mistake or the like).

| 0           |                                                                                                                                                          |        | ) Þ     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| 8<br>0<br>0 | NII ◎ △ △ A ▼ < <filter>&gt;</filter>                                                                                                                    |        |         |

| = T         | JD Message                                                                                                                                               |        | Ê       |

|             | • 204019 Generated file adder4.vo in folder "/export/home/lab3/le3a/TA/yano/le3atest/simulation/modelsim/" for EDA simulation tool                       |        |         |

|             | • 204019 Generated file adder4_7_1200mv_100c_v_slow.sdo in folder "/export/home/lab3/le3a/TA/yano/le3atest/simulation/modelsim/" for EDA simulation tool |        |         |

|             | • 204019 Generated file adder4_7_1200mv40c_v_slow.sdo in folder "/export/home/lab3/le3a/TA/yano/le3atest/simulation/modelsim/" for EDA simulation tool   |        |         |

|             | • 204019 Generated file adder4_min_1200mv40c_v_fast.sdo in folder "/export/home/lab3/le3a/TA/yano/le3atest/simulation/modelsim/" for EDA simulation tool |        |         |

|             | 204019 Generated file adder4_v.sdo in folder "/export/home/lab3/le3a/TA/yano/le3atest/simulation/modelsim/" for EDA simulation tool                      |        |         |

| Þ           | <ul> <li>Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning</li> </ul>                                                                 |        |         |

| ages        | 0 293000 Quartus Prime Full Compilation was successful. 0 errors, 13 warnings                                                                            |        | -       |

| 2 ag        |                                                                                                                                                          |        |         |

| es          | vstem Processing (127)                                                                                                                                   |        |         |

| Σ           | Horeshight (12)                                                                                                                                          | 100% 0 | 0.00.21 |

- Check the result of synthesis with Compilation Report.

- Processing -> Compilation Report or Ctrl+R

- Investigate the particulars of each item on your own.

|                                                                                                                                                                       | ler4.v X                                                                          | Compilation Report - adder4bit                                                                                                                                                                                                                                                                                          | X                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table of Contents                                                                                                                                                     | ₽ @                                                                               | Flow Summary                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                      |

| Flow Summar<br>Flow Settings<br>Flow Non-Def<br>Flow Elapsed<br>Flow Co Sum<br>Flow Log<br>Analysis & Sy<br>Flitter<br>EDA Netlist W<br>Flow Message<br>Flow Suppresi | ault Global Settings<br>Time<br>mary<br>rnthesis<br>ming Analyzer<br>rriter<br>es | Flow Status<br>Quartus II 32-bit Version<br>Revision Name<br>Top-level Entity Name<br>Family<br>Device<br>Timing Models<br>Total logic elements<br>Total combinational functions<br>Dedicated logic registers<br>Total registers<br>Total pins<br>Total memory bits<br>Embedded Multiplier 9-bit elements<br>Total PLLs | Successful - Wed Apr 12 16:20:56 2017<br>13.0.1 Build 232 06/12/2013 SP 1 SJ Full Ver<br>adder4bit<br>adder4<br>Cyclone IV E<br>EP4CE30F23I7<br>Final<br>6 / 28,848 ( < 1 % )<br>6 / 28,848 ( < 1 % )<br>0 / 28,848 ( 0 % )<br>0<br>14 / 329 ( 4 % )<br>0<br>0 / 608,256 ( 0 % )<br>0 / 132 ( 0 % )<br>0 / 4 ( 0 % ) |

|                                                                                                                                                                       |                                                                                   | L L                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                      |

- Circuit size: Fitter -> Summary

- Usage of each block on the FPGA

- If any item is over 100%, it will not fit on the FPGA device.

- Operating speed and delay: TimeQuest Timing Analyzer

- If you set set\_max\_delay and set\_min\_delay in the Synopsys Design Constraints (SDC), you can display the propagation delay time (in ns) from each input pin to each output pin (refer to the FAQ).

- If the input clock is specified in the design of the sequential circuit, the operating frequency, etc. can also be displayed. (We are working on a combinational circuit now, so more on that later.)

- If there are items in red, timing constraints have not been met.

- Unconstrained Paths will disappear if set\_max\_delay and set\_min\_delay are set appropriately.

In sequential circuit design, it is necessary to pay special attention to this.

- Specify the clock and set timing constraints (setup time to register input, hold time, propagation delay, etc.).

- I will only explain the basic clock specification; please look into the details on your own.

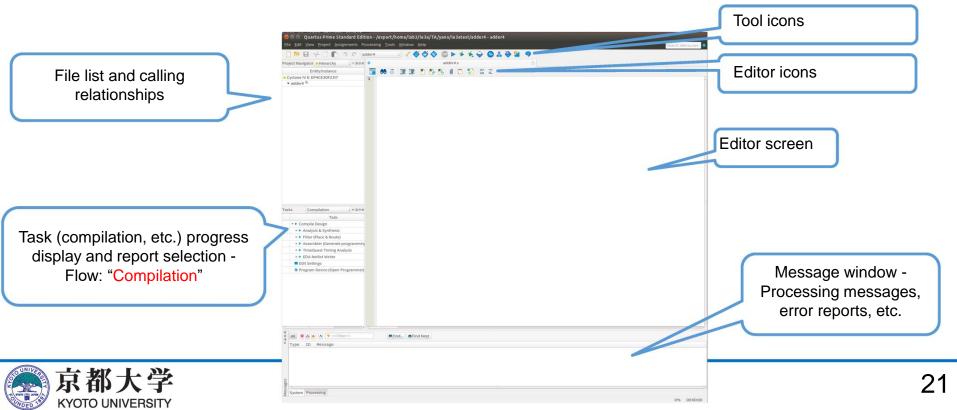

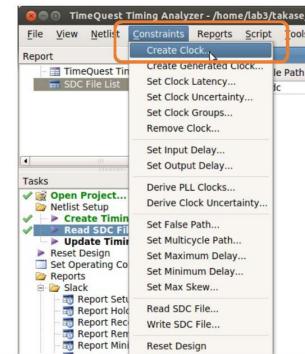

- Use "TimeQuest Timing Analyzer"

- Navigate to Tools -> TimeQuest Timing Analyzer or "TimeQuest Timing Analyzer" on Tool Icons

- TimeQuest Timing Analyzer

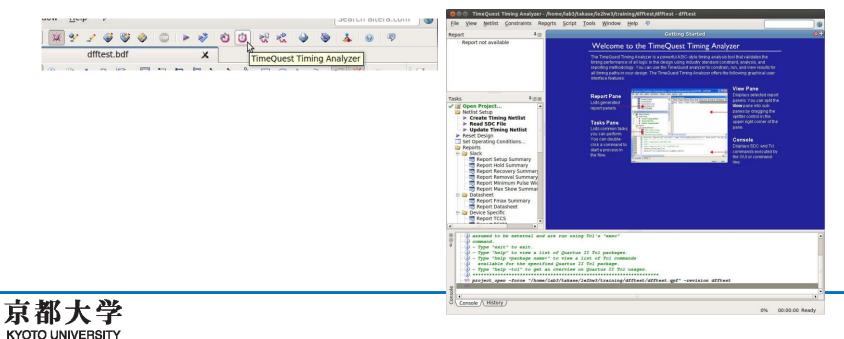

- Execute "Netlist Setup -> Create Timing Netlist" in the Tasks window.

- Execute "Netlist Setup -> Read SDC File" in the Tasks window.

- Set the clock from Constraints -> Create Clock...

- Type "help package name>" to vie

available for the specified Quart

- TimeQuest Timing Analyzer

- Set the clock from Constraints -> Create Clock...

- $\checkmark$  Clock name: Define clock name, can be left blank (e.g. clock).

- $\checkmark$  Period: Set clock period.

- ✓ Waveform edges: Set rise/fall time.

- $\checkmark$  Targets: Select the clock on the design circuit.

- Display from "List" and select with ">

- ✓ The constraints generated are displayed in SDC command.

| Create Clock                                           |                      |           |       | Matches                                                                         |                     |

|--------------------------------------------------------|----------------------|-----------|-------|---------------------------------------------------------------------------------|---------------------|

| eriod: 10.000<br>Waveform edges<br>Rising:<br>Falling: | ns ns                | 0.00 5.00 | 10.00 | 14 matches found<br>Q1[3]<br>Q2[0]<br>Q2[1]<br>Q2[2]<br>Q2[2]<br>Q2[2]<br>Q2[2] | 1 selected name     |

| argets: DC command: create                             | _clock -period 10.00 |           | Help  | data[1]<br>data[2]<br>SDC command: [get_ports {cloc                             | k}]<br>OK Cancel He |

Name Finder

Collection: get\_ports

Case-insensitive

Options

- TimeQuest Timing Analyzer

- Various reports on timing will be reported under Reports/.

- $\checkmark$  If you are not satisfied with any of them, you can add constraints.

- $\checkmark$  You can also check the reports in the Compilation Report.

- Fmax Summary: The maximum frequency at which the system can operate (depending on the constraints you provide)

- ✓ Clocks: Clock frequency of the design circuit at the current setting

- Save the constraint file by clicking "Write SDC File..." in the Tasks window.

- ✓ If you name it <module>.sdc, it will be automatically recognized by the project. (It is better to remove the .out.)

- ✓ Once you get used to it, you can create a text-based constraint file and edit it.

| SDC file name: | dfftest.sdc     |                 |     |

|----------------|-----------------|-----------------|-----|

| Expand         |                 |                 |     |

| cl command:    | write_sdc -expa | and "dfftest.so | dc" |

- Use a waveform editor to check if the logic circuit you designed works correctly.

- Use "ModelSim-Intel FPGA Starter Edition (modelsim-ase)"

- ✓ Note that modelsim-ae is also available (it does not work due to licensing constraints).

- First, configure the setting so that modelsim-ase is called from Quartus.

- Assignment -> Settings -> EDA Tool Settings -> Simulation

- ✓ Tool name: ModelSim-Altera

- ✓ Format for output netlist: Verilog HDL

- Select VHDL when designing with VHDL.

- ✓ NativeLink settings: Compile test bench

- ✓ Select "Test Benches..."

| General                                                                                        | Simulation                                                                              |    |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----|

| Files<br>Libraries                                                                             | Specify options for generating output files for use with other EDA tools.               |    |

| <ul> <li>Operating Settings and Condition</li> <li>Voltage</li> <li>Temperature</li> </ul>     | Tool name: ModelSim-Altera                                                              | 1  |

| Compilation Process Settings                                                                   | Run gate-level simulation automatically after compilation                               |    |

| Early Timing Estimate                                                                          | EDA Netlist Writer settings                                                             |    |

| Physical Synthesis Optimizat<br>EDA Tool Settings                                              | Format for output netlist: Verilog HDL                                                  | \$ |

| <ul> <li>Design Entry/Synthesis</li> <li>Simulation</li> </ul>                                 | Output directory: simulation/modelsim                                                   |    |

| Formal Verification                                                                            | Map illegal <u>H</u> DL characters <u>E</u> nable glitch filtering                      |    |

| - Analysis & Synthesis Settings<br>- VHDL Input<br>- Verilog HDL Input<br>- Default Parameters | Options for Power Estimation                                                            |    |

|                                                                                                | Generate Value Change Dump (VCD) file script     Script Settings  Design instance name: |    |

| Fitter Settings<br>TimeQuest Timing Analyzer                                                   |                                                                                         |    |

| Assembler<br>Design Assistant                                                                  | More EDA Netlist Writer Settings                                                        |    |

| SignalTap II Logic Analyzer                                                                    | NativeLink settings                                                                     |    |

| PowerPlay Power Analyzer Sett                                                                  | 0 N <u>o</u> ne                                                                         |    |

|                                                                                                | Compile test bench:                                                                     | s  |

|                                                                                                | Use script to set up simulation:                                                        |    |

|                                                                                                | O Script to compile test bench:                                                         |    |

31

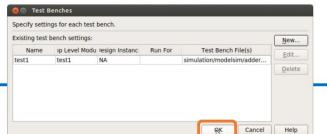

- First, configure the setting so that modelsim-ase is called from Quartus.

- Test Benches

- ✓ Select "New..."

- New Test Bench Settings

- ✓ Test bench name: Give it a name and create a new one.

- ✓ If you set the "Top level module in test bench:" to the actual test bench module name (<module>\_vlg\_tst if you use Template Writer), you will not get the "Error loading design" message on the first run of ModelSim.

- Test bench and simulation files: simulation/modelsim/<module>\_test1.vt (.vht for VHDL)

- Create an empty file from the terminal.

- ✓ Select "Add"

- Return to Test Benches and select OK.

| 😣 🗊 Edit Test Bench Settings                            |             |  |  |  |  |  |

|---------------------------------------------------------|-------------|--|--|--|--|--|

| Edit test bench settings for the selected test bench.   |             |  |  |  |  |  |

| Test bench name: test1                                  |             |  |  |  |  |  |

| Top level module in test bench: test1                   |             |  |  |  |  |  |

| Use test bench to perform VHDL timing simulation        |             |  |  |  |  |  |

| Design instance name in test bench: NA                  |             |  |  |  |  |  |

| Simulation period                                       |             |  |  |  |  |  |

| Run simulation until all <u>vector stimuli</u> are used |             |  |  |  |  |  |

| ○ End simulation at: 5 \$                               |             |  |  |  |  |  |

| Test bench and simulation files                         |             |  |  |  |  |  |

| File name simulation/modelsim/adder4_test1.vt           | <u>A</u> dd |  |  |  |  |  |

| File Name Library HDL Version                           | Remove      |  |  |  |  |  |

|                                                         | Up          |  |  |  |  |  |

|                                                         | Down        |  |  |  |  |  |

|                                                         | Properties  |  |  |  |  |  |

| OK Cance                                                | I Help      |  |  |  |  |  |

32

Once you get used to it, you don't need to bother creating a template.

- Create a test bench file.

- Processing -> Start -> Start Test Bench Template Writer

- ./simulation/modelsim/<module>.vt will be created.

- Copy it to ./simulation/modelsim/<module>\_test1.vt, etc.\$ cp ./simulation/modelsim/adder4.vt ¥

./simulation/modelsim/adder4\_test1.vt ¥

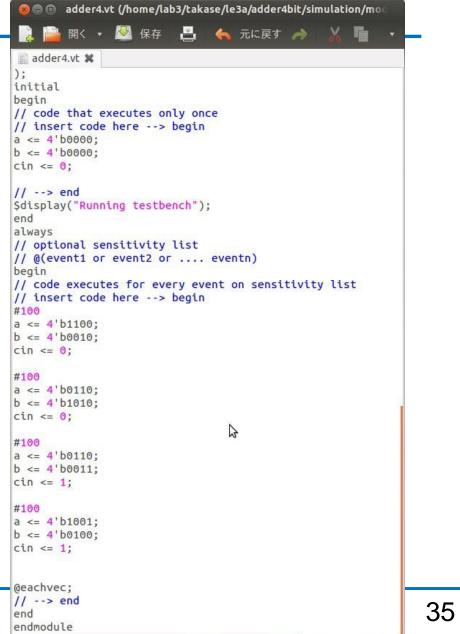

- Edit <module>\_test1.vt so that you have the desired input waveform.

- $\checkmark$  Change the time unit (default is ps, which is too fast).

- `timescale <mark>1 ns</mark> / 1 ps

- ✓ Describe the default settings directly under the following description.

- // code that executes only once

- // insert code here --> begin

- ✓ Describe the desired value (waveform) directly under the following description.

- // code that executes for every event on sensitivity list

- // insert code here --> begin

- Example of test bench file notation

- Assignment: // 1 bit A <= 0; B <= B + 1; // bitwise operation Cin <= ~Cin; // 4-bit binary number As <= 4'b10\_01; // 4-bit binary number As <= 4'b10\_01;</li>

- Assigned in parallel (if there is no delay).

- Delay: #1000 Notation is the same with Verilog HDL.The explanation for VHDL is omitted.

Iteration:

always begin

#100

clock <= ~clock;</li>

end

- ✓ Useful for generating clock waveforms.

- Must be written outside of "initial begin end" or "always begin end," and inside of "module endmodule."

- ✓ always blocks are executed in parallel with each other.

- ✓ Conditional statements can be written using @().

- Example of test bench file description

- The time unit has also been changed.

`timescale 1 ns / 1ps

- Think carefully about units and delays.

- ✓ If it is too small?

- Recompile the design (the task window should show a ?).

- Start the simulator.

- Tools -> Run Simulation Tool -> Gate Level Simulation...

- Timing model: Run "Slow -7 1.2V 100 Model"

| g <u>T</u> ools <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                         |                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------|

| Run Sim <u>u</u> lation Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RTL Simulation                                                          |                                                       |

| Image: Complete Simulation Library Compiler         Image: Complete Simulation Complete Simulatination Complete Simulation Complete Simulation Comple                          | <u> </u>                                                                | tion f                                                |

| Image: Image of the second | Status<br>rtus II 32-bit Version<br>sion Name                           | Success<br>13.0.1 B<br>fulladde                       |

| <ul> <li>Chip Planner</li> <li>Design Partition Planner</li> <li>Netlist Viewers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | level Entity Name<br>ily<br>ce<br>ng Models                             | fulladder<br>Cyclone<br>EP1C6Q2<br>Final              |

| <ul> <li>SignalTap II Logic Analyzer</li> <li>In-System Memory Content Editor</li> <li>Logic Analyzer Interface Editor</li> <li>In-System Sources and Probes Editor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l logic elements<br>l pins<br>l virtual pins<br>l memory bits<br>l PLLs | 2 / 5,980<br>5 / 185 (<br>0<br>0 / 92,10<br>0 / 2 ( 0 |

| 😣 🗊 🛛 EDA Ga  | te Level Simulation         |     |

|---------------|-----------------------------|-----|

| Timing model: | "Slow -7 1.2V 100 Model" \$ | Run |

- Start the simulator.

- The circuit you have designed is located under gate\_work in the Library.

- ✓ A link to gate\_work will be under "work."

- Recompile the test bench file just in case.

- Right-click on gate\_work -> <module>\_vlg\_tst in the "Library" window and click "Recompile."

- ✓ You will get "# Error loading design" right after startup, but don't worry about it. It will go away after recompiling.

- $\checkmark\,$  You need to recompile every time you rewrite the test bench.

| 😣 🖨 🗊 ModelSim ALT                                                                                                                      | ERA STARTER EDITION 10.1d                                                              |                  |    |                       |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|----|-----------------------|

| <u>Eile Edit View Compile S</u>                                                                                                         | jimulate A <u>d</u> d <b>Library</b> T <u>o</u> ols Layo <u>u</u> t Boo <u>k</u> marks | : <u>W</u> indow |    | Help                  |

| 🛛 - 🚘 🖬 🛸   🐰                                                                                                                           | 🖻 🏙 👱 🔔   🖉 - 🖊 🖺 🗖 🛛 🗳 🕮 (                                                            | Q 🕱              |    |                       |

| Layout Simulate                                                                                                                         | ColumnLayout AllColumns                                                                |                  |    | ╋ <b>╗ ┣ ┟┟</b> ┶┱ぇぇぇ |

|                                                                                                                                         |                                                                                        |                  | ·  |                       |

| 📶 Library 💳 🛲 🕂 🗗 🛛                                                                                                                     |                                                                                        | R Wave - Default |    |                       |

| ▼ Name                                                                                                                                  | Value Kind                                                                             | 🌜 🗸 Ms           | 38 |                       |

| ● dt, 220model_ver Simula<br>● dt, attera Simula<br>● dt, attera_Insim Edit<br>● dt, attera_Insim_ver Bofera<br>● dt, attera_mir Person | we without Optimization<br>te with full Optimization<br>ite with Coverage              |                  |    |                       |

| 京都大学 attera ver<br>Update                                                                                                               | 78 😼                                                                                   |                  |    |                       |

Starting simulation

YOTO UNIVERSIT

- Simulate -> Start Simulation...

- In the Design tab, under "Design Unit(s)," select gate\_work.<module>\_vlg\_tst.

- In the Libraries tab, under "Search Libraries," click Add... to add the necessary libraries.

- $\checkmark$  Select "cycloneive\_ver" and "altera\_ver" in advance.

| ModelSim ALTERA STARTER EDITION 10.1d Elle Edit View Compile Simulate Agd Library Tools Layor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 😣 🗈 Start Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                    | Start Simulation                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Ene gent giver guinning summary Aud Library igos Layo       Image: Start Simulation       Layout Simulatie       Start Simulation       Start Simulation       Image: Start Simulation | Design VHDL Verilog Libraries Name Type An work Library A gate_work Library A gate_work Library A doted Module A 220model Library A attera Lib | Path<br>gate_work<br>/home/lab3/lakase/le3a/adder4bit<br>e /home/lab3/lakase/le3a/adder4bit<br>sMODEL_TECH/./altera/vhdl/22(<br>\$MODEL_TECH/./altera/vhdl/alte<br>\$MODEL_TECH/./altera/vhdl/alte | Design VHDL Verilog Libraries SDF Others<br>Search Libraries (-L)<br>altera_ver<br>cycloneive_ver<br>gate_work<br>work<br>Select Library          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Design Unit(s) [gate_work.adder4_vlg_tst Optimization Fnable optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P<br>Resolution<br>Ips                                                                                                                                                                             | Cycloneive_ver<br>cycloneiv_pcie_hip<br>cycloneiv_pcie_hip_ver<br>cycloneiv_ver<br>Cycloneive_ver<br>Cycloneive_ver<br>Cycloneive_ver<br>K Cancel |

| 京都大学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OK Cancel                                                                                                                                                                                          | OK Cancel                                                                                                                                         |

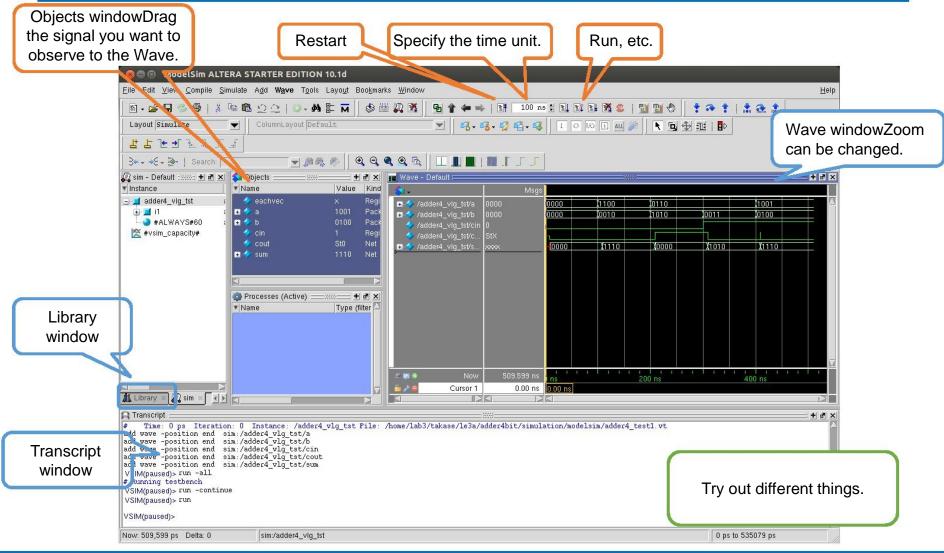

- Running simulation

- Drag the signal line you want to observe from the "Objects" window to the "Wave" window.

- Set the "Run Length" to the desired size (e.g. 100 ns).

- $\checkmark$  If it is too large, the simulation time will increase.

- Click "Run," "Run All," etc.

- You can also type directly in the "Transcript" window (this way may be faster once you get used to it).

- Zoom In/Out/Full etc. of the waveform display can be changed by rightclicking or typing.

- Waveforms are already specified in the test bench, but can also be specified directly.

- ✓ Right-click on a signal line and select "Force....," etc.

- If you have changed the test bench, recompile it from the "Library" window and "Restart."

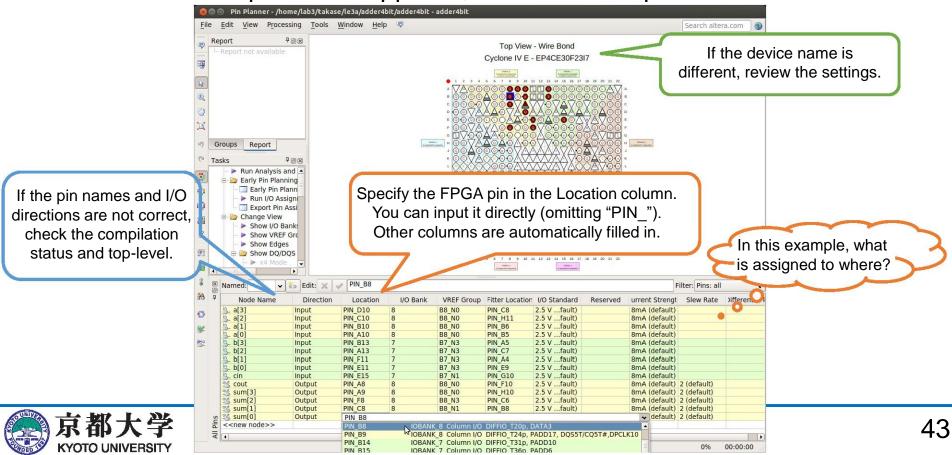

# g. Assignment of I/O Pins

- Assign the signal lines of the circuit to the I/O pins of the FPGA.

- Depending on the assignment, you can provide input from switches on the board or output signals to LEDs.

- Refer to the <u>user's manual and pin assignment table</u> to see which module corresponds to which I/O pin.

- For the correspondence between the I/O pins of the FPGA and various types of devices, read the user's manual and pin assignment table carefully.

- In this example, the two input values are DIP SW A and B, the carryin is the numpad push SW SW4, and the sum and carry-out are LEDs.

- Feel free to change the above pin assignments in any way that makes it easier for you.

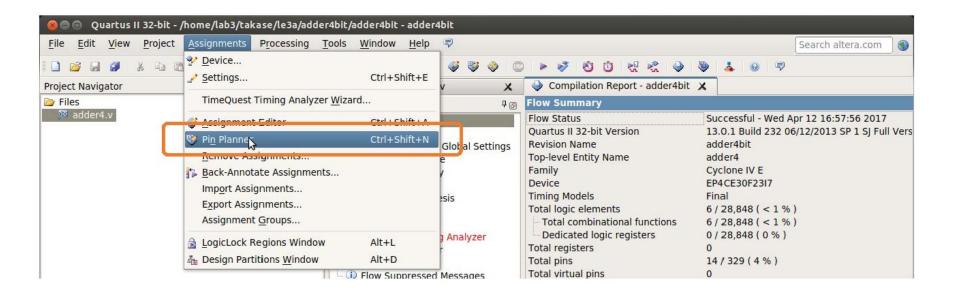

## g. Assignment of I/O Pins

- Boot up "Pin Planner"

- "Assignments" -> "Pin Planner" or Ctrl+Shift+N

## g. Assignment of I/O Pins

- Assigning I/O pins

- Recompile the design if the name of the pin does not appear.

- If another pin name appears, check if it is top-level.

- Write the synthesized circuit image to the FPGA and verify the operation on the actual device.

- The design is not complete until it works on the actual device!

- If the Tasks window shows a yellow ?, recompile; if it shows a red

×, debug the HDL code, etc. since it is an error.

- Preparing the FPGA board

- Connect the power supply cable.

- Connect the USB cable to the PC.

- Turn on the board (switch on extension cable).

- If the USB cable is not recognized, please refer to this FAQ.

- Launching the FPGA writing tool

- "Tools" -> "Programmer" or "Program Device (Open Programmer)" in the Tasks window

| Quartus II 32-bit - /home/lab3/takase/le3a/add<br>File Edit View Project Assignments Processing      | Tools Window Help 🖓                                                                                                                                                                                 |                                                                                                                                                                                                     | Search altera.com                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rie gut view rigett Assignments rigetssing<br>□ ☞ 교 교 ▲ ▲ ພ ພ → ペ adder4bit<br>Project Navigator #⊗g | Run Simulation Tool                                                                                                                                                                                 | Compilation Report - adder4bit                                                                                                                                                                      | <u> </u>                                                                                                                                                                      |

| 30 adder4.v                                                                                          | <ul> <li>TimeQuest Timing Analyzer</li> <li>Advisors</li> <li>Chip Planner</li> <li>Design Partition Planner</li> <li>Netlist Viewers</li> </ul>                                                    | Flow Status<br>Quartus II 32-bit Version<br>Revision Name<br>Top-level Entity Name<br>Family<br>Device<br>Timing Models<br>Total logic elements                                                     | Successful - Wed Apr 12 17:51:01 2017<br>13.0.1 Build 232 06/12/2013 SP 1 SJ Full Ver<br>adder4bit<br>adder4<br>Cyclone IV E<br>EP4CE30F23I7<br>Final<br>6 / 28.848 ( < 1 % ) |

|                                                                                                      | SignalTap II Logic Analyzer In-System Memory Content Editor I Logic Analyzer Interface Editor In-System Sources and Probes Editor SignalDrobe Dire Programmer Content State State State State State | Total combinational functions     Dedicated logic registers     Total registers     Total pins     Total virtual pins     Total memory bits     Er bedded Multiplier 9-bit elements     Tr tal PLLs | 6 / 28,848 ( < 1 %)<br>0 / 28,848 ( 0 % )<br>0<br>14 / 329 ( 4 % )<br>0<br>0 / 608,256 ( 0 % )<br>0 / 132 ( 0 % )<br>0 / 4 ( 0 % )                                            |

| ▲ Hierarchy Files P Design Units C IP Co                                                             | Transceiver Tool <u>k</u> it                                                                                                                                                                        |                                                                                                                                                                                                     |                                                                                                                                                                               |

| Flow: Compilation                                                                                    | External Memory Interface Toolkit     MegaWizard Plug-In Manager     Nios II Software Build Tools for Eclipse     Qsys     Tcl Scripts     Customize     Options     License Setup                  |                                                                                                                                                                                                     |                                                                                                                                                                               |

|                                                                                                      | Install Devices                                                                                                                                                                                     | -                                                                                                                                                                                                   |                                                                                                                                                                               |

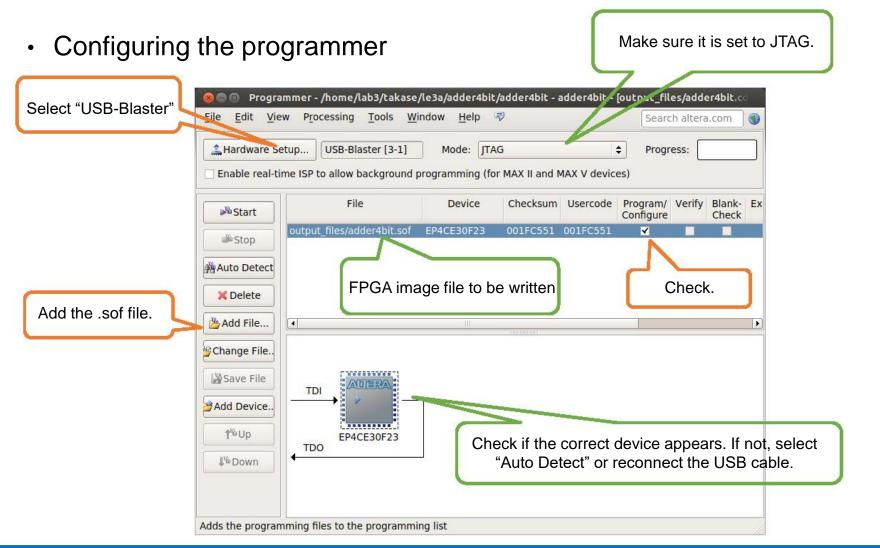

- Configuring the programmer

- Click "Hardware Setup" and select "USB-Blaster [1-1]" under "Currently selected hardware:"

- ✓ If USB-Blaster does not appear in the Available hardware items, reconnect the PC to USB. If USB-Blaster still doesn't appear, you may have a device driver problem, so ask a TA.

- Set the Mode to "JTAG."

- If the file is not displayed in the list, select the file to be written from the Add File...

- √ ./output\_files/<proj\_name>.sof

- Check Program/Configure on the list.

| hardware setup applies only to |          |            | ing devices. This programming<br>w. |

|--------------------------------|----------|------------|-------------------------------------|

| Currently selected hardware:   | No Hards |            |                                     |

| Available hardware items       | USB-Blas | iter [3-1] |                                     |

| Hardware                       | Server   | Port       | Add Hardware                        |

| USB-Blaster                    | Local    | 3-1        | Remove Hardware                     |

|                                |          |            |                                     |

- Writing the circuits to the FPGA

- Click "Start"

- When "Process:" shows "100% (Success)" in green, the writing process is completed. achine

- Verifying the behavior on the actual machine

- If the desired behavior is correct, you are finished!

| See Progra          | mmer - /home/lab3/takase<br>w P <u>r</u> ocessing <u>T</u> ools <u>W</u> |            | /adder4bit - a<br>₽ | idder4bit - |                       | es/adde  | ien an Aonaine an Aonaine an Aonaine an Aonaichtean Aonaichtean Aonaichtean Aonaichtean Aonaichtean Aonaichtean |    |

|---------------------|--------------------------------------------------------------------------|------------|---------------------|-------------|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------|----|

| Hardware Se         | etup USB-Blaster [3-1]<br>me ISP to allow background                     | Mode: JTA  |                     |             | Progr<br>es)          | ress: 0% | 6 (Succe                                                                                                        | ss |

| Start               | File                                                                     | Device     | Checksum            | Usercode    | Program/<br>Configure | Verify   | Blank-<br>Check                                                                                                 |    |